MEMÓRIAS...

...Săo dispositivos eletrônicos utilizados para armazenar dados.

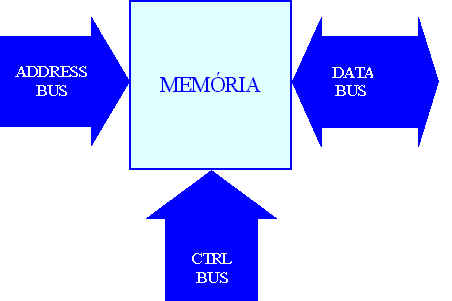

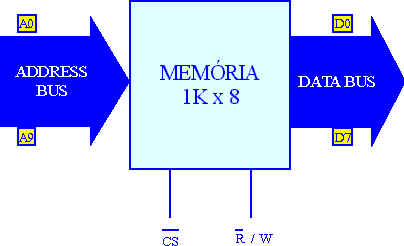

Estrutura genérica de uma memória

Barramento de Dados ou Data Bus:

Temos a informaçăo a ser lida ou armazenada no endereço .

Barramento de Endereço ou Address Bus:

Fornece a posiçăo da memória que se desejamos acessar,para realizar operaçăo de leitura ou escrita.

Barramento de Controle ou Control Bus:

É formado por sinais que controlam o funcionamento da Memória: Chip Select, Escrita, Leitura, Programaçăo etc.

Características das Memórias:

a) Capacidade de armazenamento = tamanho da palavra binária x número de posiçőes da memória.

b) Tempo de Acesso = tempo necessário para obtermos os dados na saída no ciclo de leitura.

Exemplo para maiores esclarecimentos:

Em uma memória cujo arranjo é de 1K x 8 temos:

a)1K é o número de posiçőes de memória, ou ainda, 1024 posiçőes;8 é o tamanho de palavra binária em cada posiçăo da memória.

b)Capacidade = 8K bits ou 1K Byte

c)Via de Dados = 8 bits, ou seja, de D0 a D7

d)Via de Endereços = 10 bits ( 2n =1024 ; entăo n=10 ) , ou seja, A0 a A9.

Em bloco:

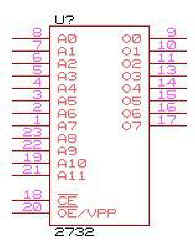

Exemplo de um chip de memória de 64K ( CI 27C64 )

Temos aqui uma memória do tipo EPROM, cujo arranjo é 8K x 8bits, ou seja, possui 13 vias de endereços, A0 a A12, 8 vias de dados, O0 a O7 e seus sinais de controle. Observe a numeraçăo da pinagem do CI, ou seja, pino 1=VPP onde este é o primeiro pino localizado na parte superior esquerda do chip. Sendo assim o restante da numeraçăo da pinagem se dá sequencialmente, ou seja, o último pino na parte inferior esquerda será o pino 14, o último pino na parte inferior direita será o pino 15 e o primeiro pino na parte superior direita será o pino 28. Tręs pinos năo aparecem no diagrama de pinagens, esses săo pinos (+VCC e GND) de alimentaçăo da memória.

| Capacidade | número de posiçőes da memória | número de linhas no Address Bus | Via de Endereços | tamanho da palavra binária em cada posiçăo de memória | Via de Dados |

| 1Kx8 | 1024 | 10 | A0 - A9 | 8 bits | D0 - D7 |

| 512x4 | 512 | 9 | A0 - A8 | 4 bits | D0 - D3 |

| 16Kx8 | 16K | 14 | A0 - A13 | 8 bits | D0 - D7 |

| 32Kx1 | 32K | 5 | A0 - A4 | 1 bit | D0 |

| 256kx4 | 256K | 18 | A0 - A17 | 4 bits | D0 - D3 |

Tipos de Memórias

| Memórias NĂO voláteis | Memórias voláteis |

| ROM Máscara | RAM Estática (SRAM) |

| PROM | RAM Dinâmica (DRAM) |

| EPROM | |

| EEPROM |

ROM Máscara

READ ONLY MEMORY (Memória Somente de Leitura). Săo memórias nas quais as informaçőes săo gravadas na sua fabricaçăo, por isso o nome ROM Máscara. O dispositivo se comporta como um circuito combinacional, podendo gerar várias tabelas verdades.

PROM

PROGRAMMABLE READY ONLY MEMORY (Memória Programável Somente de Leitura). A programaçăo nesta memória pode ser feita pelo usuário. Uma vez programada,a PROM năo pode mais ter o seu conteúdo alterado.

EPROM

ERASABLE PROGRAMMABLE READ ONLY MEMORY (Memória programável e apagável Somente de Leitura). Sua programaçăo é feita eletricamente e apagada através da exposiçăo de sua pastilha semicondutora ŕ luz Ultravioleta. Esta exposiçăo é possível devido ao fato do encapsulamento possuir uma janela transparente sobre a pastilha. O tempo de exposiçăo varia em torno de 10 a 45 minutos.

Descriçăo básica do processo de gravaçăo de uma EPROM 2732, que é uma EPROM de 4Kx8 bits

| Para realizar operaçăo de ... | CE - Chip Enable | OE/Vpp - Output Enable | Data Bus |

| ...Leitura | LOW | LOW | D out |

| ...Programaçăo | Pulso 50ms | +25V | D in |

| ...Inibiçăo | HIGH | 5V | HIGH - Z |

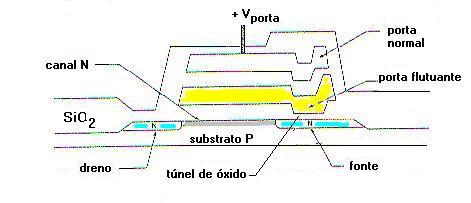

EEPROM ou E˛PROM

ELETRICCALLY ERASABLE PROGRAMMABLE READ ONLY MEMORY (Memória Programável e Apagável Eletricamente Somente de Leitura). Também utiliza o conceito de porta flutuante.Podemos realizar o mecanismo de escrita e apagamento sem precisar retirar o chip do circuito.

A maior vantagem da EEPROM sobre a EPROM é a possibilidade de apagamento e reprogramaçăo de palavras individuais,em vez da memória toda.O apagamento de uma EEPROM é realizado eletricamente,de uma forma mais rápida(10 ms) e no próprio circuito,contra mais ou menos 30 minutos de uma EPROM(que deve ser retirada do circuito e é apagável com luz ultra-violeta).

Uma EEPROM também pode ser programada bem mais rapidamente do que uma EPROM.

A figura a seguir mostra o transistor Mosfet básico da memória EEPROM.Observe que a porta flutuante tem uma parte saliente bem próxima da fonte do transistor Mosfet,possibilitando a característica do apagamento por eletricidade.A aplicaçăo de uma tensăo adequada entre a porta do Mosfet e a fonte(Vporta>Vfonte) fará com que elétrons sejam forçados para a porta flutuante.Tal carga năo desaparecerá,mesmo depois de removida a tensăo.A aplicaçăo de uma tensăo adequada Vporta<Vfonte irá remover os elétrons da porta flutuante,apagando a célula de memória.

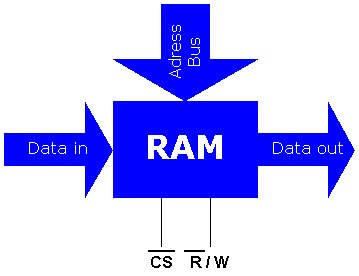

RAM

RANDOM ACCESS MEMORY (Memória de Acesso Aleatório).

É uma memória volátil de escrita e leitura.

Esta memória é de acesso aleatório porque permite o acesso direto a qualquer posiçăo para leitura ou escrita. Existem 2 tipos de memórias RAM: RAM Estática (SRAM) e RAM Dinâmica (DRAM).

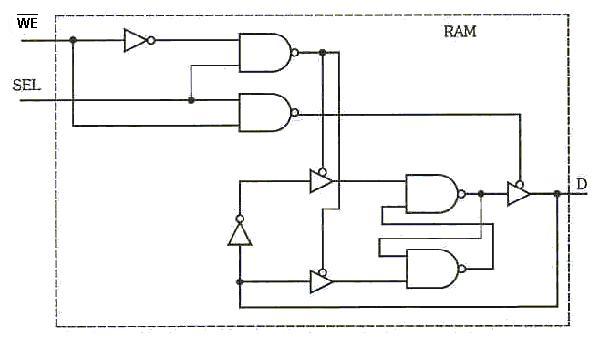

Estrutura de uma memória RAM

SRAM (STATIC RAM)

Neste tipo de memória a célula é formada basicamente por um Flip-Flop.A informaçăo do bit nesta célula mantém seu valor até o próximo ciclo de escrita (desde que mantida a alimentaçăo). Possui baixo tempo de acesso.

Exemplo de memória RAM ( CI 6116- 2Kx8 bits )

Descriçăo da Pinagem:

| Pino | Descriçăo |

| A0 - A10 | Adress Bus |

| D0 - D7 | Data Bus |

| CE | Chip Enable (Ativo em "0"=Habilita Memória) |

| OE | Output Enable (Ativo em "0"=Habilita Leitura de Dados) |

| WE | Write Enable (em"0"=Habilita Escrita,em"1"=Leitura) |

Funcionamento dos Controles (Control Bus)

| CE | OE | WE | Status da Memória |

| 0 | 0 | 1 | Habilita Leitura |

| 0 | 1 | 0 | Habilita Escrita |

| 0 | 1 | 1 | Memória Desabilitada (Tri-State) |

| 1 | X | X | Memória Desabilitada (Tri-State) |

Funcionamento básico de uma célula da RAM estática:

Nos circuitos integrados as células de memória săo construídas com diversas tecnologias e circuitos, e o exemplo a seguir será apresentado devido ao seu aspecto didático.

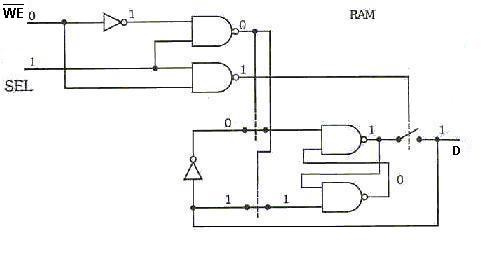

ESCRITA

Para escrever um dado, selecionamos a célula, o que é feito por um circuito de endereçamento que faz SEL = 1 e passamos o sinal de controle para escrita, WE=0. Depois aplicamos o dado no terminal D, que está entăo configurado como entrada.

A figura a seguir mostra a célula de memória nesta situaçăo.

Vemos que a porta NAND superior terá nível 0 na saída, e com isto, os buffers nas entradas do flip-flop estarăo habilitados, configurando assim um flip-flop tipo D, ao mesmo tempo a porta NAND inferior terá um nível 1 na saída fazendo com que o buffer de saída do flip-flop esteja em tri-state, de modo que o dado presente em D esteja conectado ŕ entrada do flip-flop e seja entăo armazenado.

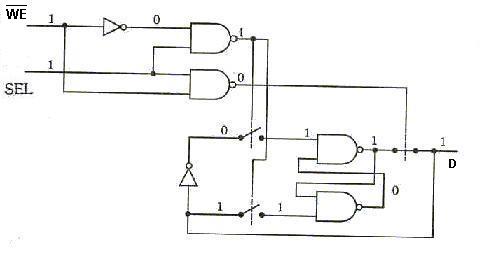

LEITURA

Para fazer a leitura, selecionamos igualmente a célula fazendo SEL=1 e colocamos WE=1, assim o dado armazenado é obtido em D, veja na figura a seguir, a célula nesta situaçăo.

Vemos que a porta NAND superior tem nível 1 na saída, isto faz com que os buffers de entrada do flip-flop estejam em tri-state. As portas NAND que constituem o flip-flop estăo agora desconectadas (estado de alta impedância) e devido a sua característica construtiva, reconhecem esta situaçăo como um nível 1, o que faz com que o flip-flop mantenha o estado anterior (Qf = Qa). Enquanto isto, a porta NAND inferior tem nível 0 na saída, o que faz com que o buffer de saída esteja habilitado, e com isto o bit armazenado no flip-flop estará no terminal D.

No caso da célula năo ser selecionada (SEL = 0), as duas portas NAND apresentarăo nível 1 em suas saídas, deixando todos os buffers em tri-state e a célula ficará com a saída desativada (tri-state), impedindo qualquer escrita ou leitura de dados.

DRAM (DINAMIC RAM)

A diferença básica está no tipo de célula que a compőe. Enquanto na SRAM a célula de memória é composta por um Flip-Flop, na DRAM ela é formada por um transistor MOS.

Na DRAM a informaçăo é armazenada na Capacitância parasita de um transistor MOS. Devido ŕ corrente de fuga esta informaçăo pode ser perdida após um determinado tempo (de 2 a 4 ms), necessitando portanto de uma renovaçăo periódica denominada operaçăo de Refresh.

Sempre que uma operaçăo de leitura for realizada em determinado endereço,todas as células desse endereço sofrerăo um refresh( realizado por um CI controlador de DRAM )

Exemplo de DRAM

| Pino | Descriçăo |

| A0-A7 | Address Bus |

| D0 | Data out |

DI |

Data in |

| CAS | Column Address Strobe (Habilitaçăo de Endereçamento de Coluna) |

| RAS | Row Address Strobe (Habilitaçăo do Endereçamento de Linha) |

| WE | Write Enable (Habilita Escrita) |

ASSOCIAÇĂO DE MEMÓRIAS

As memórias podem ser associadas para expandir sua capacidade de dados ou de localizaçőes. Por exemplo,se tivermos memórias de 256x4bits, podemos construir uma memória de 256x8 bits, fazendo a seguinte ligaçăo:

O bus de endereçamento,o controle de leitura/escrita e a seleçăo do chip săo aplicados simultaneamente nas duas memórias.

Utilizando a mesma memória de 256x4bits, podemos expandir sua capacidade de armazenamento. A figura a seguir mostra duas memórias de 256x4 ligadas para construir uma memória de 512x4 bits.

Os endereços e o controle de leitura/escrita săo simultâneos, mas a seleçăo do chip é fornecida pela linha de endereço A8. Se A8=0, a primeira memória RAM 1 é selecionada,ficando a RAM2 com seu bus de dados em Hi-Z e se A8=1, a segunda memória RAM 2 é selecionada,ficando a RAM1 com seu bus de dados em Hi-Z. O bus de dados da RAM1 é interligada com o bus de dados da RAM2.

Entăo o endereçamento de cada memória ficaria:

Seleçăo da Memória A8 |

A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Endereço em Hexadecimal |

|

RAM 1 |

0 |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 000

|

| RAM 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0FF |

RAM 2 |

1 |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 100

|

| RAM 2 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1FF |

RESUMO

| BACK |