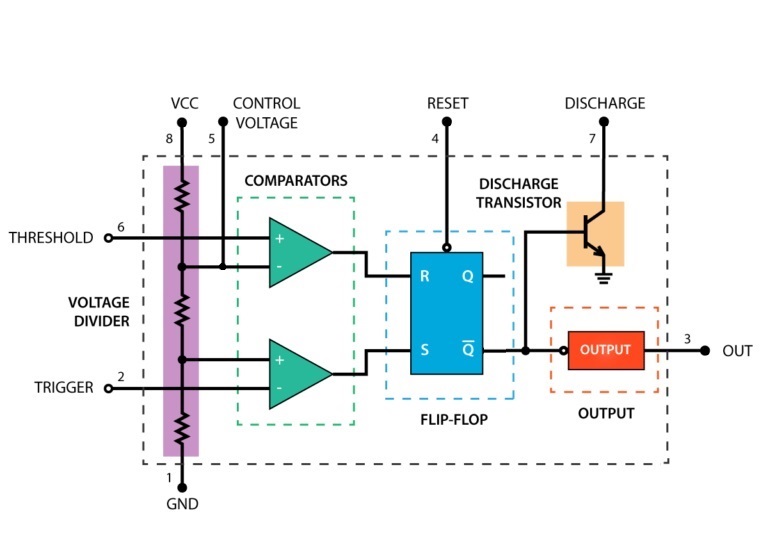

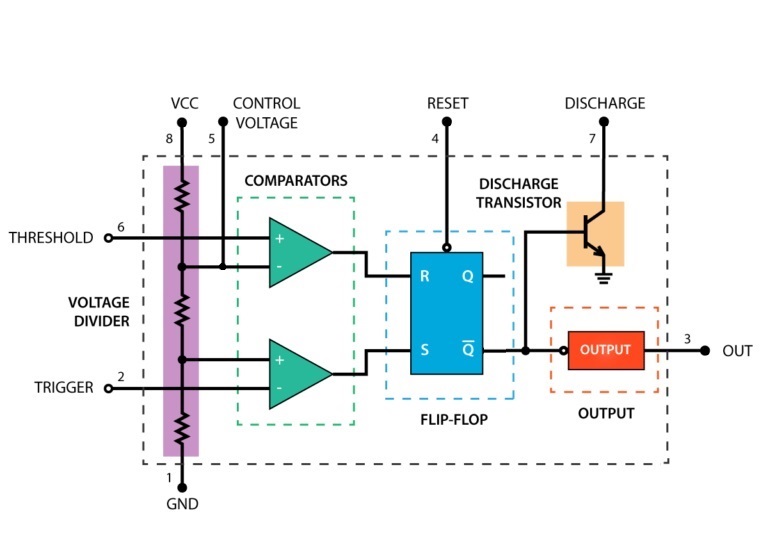

A Fig.1 mostra o diagrama em blocos do CI 555.

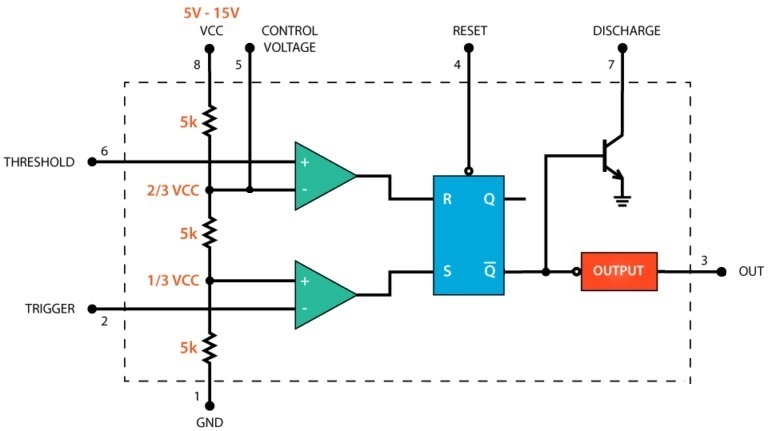

Fig.2: Esquema do circuito interno do CI 555

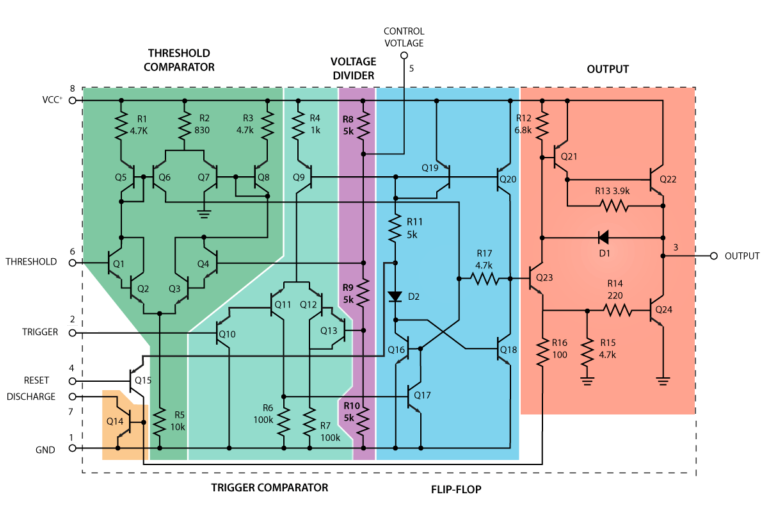

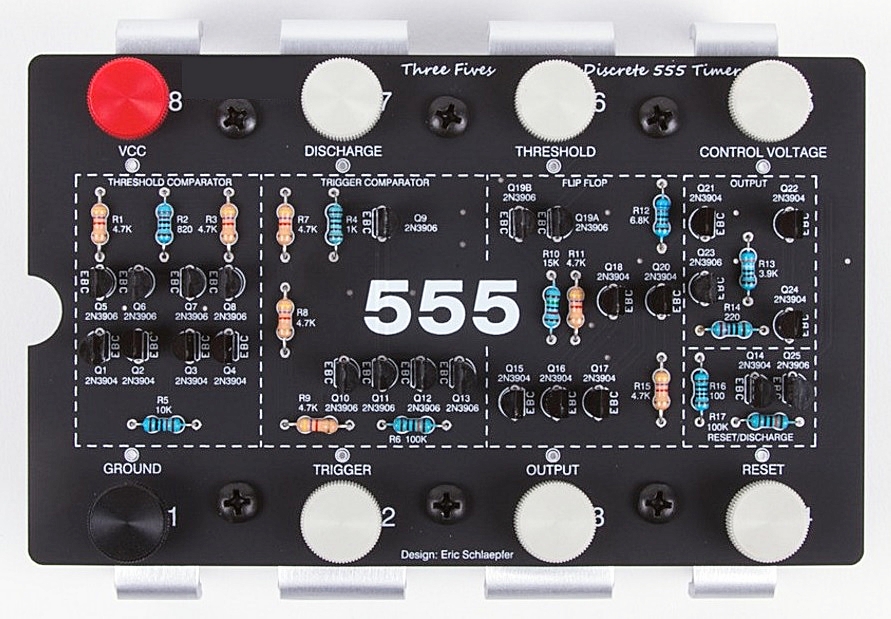

Fig.3: CI 555 montado com componentes discretos

Descrevendo cada um dos blocos do diagrama mostrado na fig.1

Comparadores ( blocos nº1 ): Num comparador a saída será alta ( nível lógico 1 ou VCC ) se V+ > V- e será baixa ( nível lógico 0 ou 0V ) se V+ £ V-. A Fig.4 mostra o comparador com a saída em nível alto e a com a saída em nível baixo.

|

Fig.4: Comparadores - Saída alta e saída baixa |

No 555 a tensão no pino 2 ( Trigger ) é sempre comparada com VCC/3, enquanto a tensão no pino 6 ( Threshold ) é comparada com 2.VCC/3.

Flip – Flop RS (bloco nº2 ): É um biestável , isto é, tem dois estados estáveis e a mudança de estado se faz de acordo com a tabela verdade dada na Fig.5.

|

|

QA´ = Estado atual QF´

= Estado futuro ? = erro lógico

|

||||||||||||||||||||

Fig.5: Símbolo do Flip Flop tipo RS e sua Tabela verdade |

||||||||||||||||||||||

Buffer de Saída (bloco nº3 ): Tem como finalidade aumentar a capacidade de corrente do CI. A corrente de saída do CI está limitada a 200mA . Observe que o buffer inverte a sua entrada, isto é, a saída do CI é Q.

|

|

| Transistor NPN

interno:

Opera saturado quando |

A alimentação ( VCC ) pode variar de 4,5V a 16V. O encapsulamento mais comum é o DIP ( Dual In line Package ).

|

|

Fig.6: Encapsulamento Dual- In - Line

|

|

| Pino | Nome |

Função |

1 |

GND = |

0V. |

2 |

TRIG = |

Disparador. Um intervalo de temporização inicia quando a entrada neste pino cai abaixo de ½ do valor em CTRL (1/3 de VCC, se CTRL não estiver sendo usado). Isto faz o valor em OUT ser ALTO. O valor ALTO em OUT será mantido enquanto este pino estiver com tensão baixa. |

3 |

OUT = |

Saída. O valor de saída, que pode ser nível lógico ALTO (até 1.7 V abaixo de +VCC) ou BAIXO (igual a GND). |

4 |

RESET = |

Reset. Reinicia o intervalo se ligado em GND. Um novo intervalo só inicia novamente se RESET tiver uma tensão de no mínimo 0,7V. |

5 |

CTRL = |

Tensão de controle. Permite estabelecer a tensão de referência usada para disparar e limitar o temporizador. Normalmente este pino não é usado (e deve ser conectado ao GND através de um capacitor de 10nF), e neste caso a tensão de referência será sempre de 2/3 de VCC. |

6 |

THR = |

Limite. Quando o nível de tensão aqui for maior que em CTRL (2/3 de VCC), o valor em OUT será reduzido para zero, terminando o ciclo. |

7 |

DIS = |

Chave de descarga. O pino é ligado temporariamente à GND entre cada intervalo de temporização. Um capacitor conectado aqui será descarregado entre intervalos. O início de novo ciclo fecha a chave que só abre novamente quando o próximo intervalo terminar (quando a tensão em OUT tiver nível lógico BAIXO). |

8 |

VCC = |

Fonte de tensão entre +3 e +15V para alimentar o CI 555. |

Os controles (entradas) disponíveis são 4: CTRL(5), RESET(4), TRIG(2) e THR(6). A entrada RESET (pino 4) tem prioridade sobre TRIG(pino 2), e TRIG(pino 2) tem prioridade sobre THR(pino 6). Isto significa que se RESET estiver acionado (ligado no negativo), os valores de TRIG e THR são ignorados, e se RESET estiver inativo (ligado no positivo), e TRIG for acionado (ligado no negativo), o valor de THR é ignorado. THR só é considerado se RESET e TRIG estiverem ambos inativos (ligados no positivo). A entrada CTRL estabelece a referência usada por TRIG e THR. Em circuitos simples, CTRL é ligada a GND através de um capacitor de 10nF (para eliminar interferências), fazendo com que a referência seja considerada igual à tensão de entrada (Vcc).

As saídas são duas: OUT(3) e DIS(7). OUT (pino 3) é usado em praticamente todas as aplicações. DIS (pino 7)é ligada ao GND (negativo) todas as vezes que um ciclo termina, e geralmente usada para descarregar um capacitor ligado neste pino.

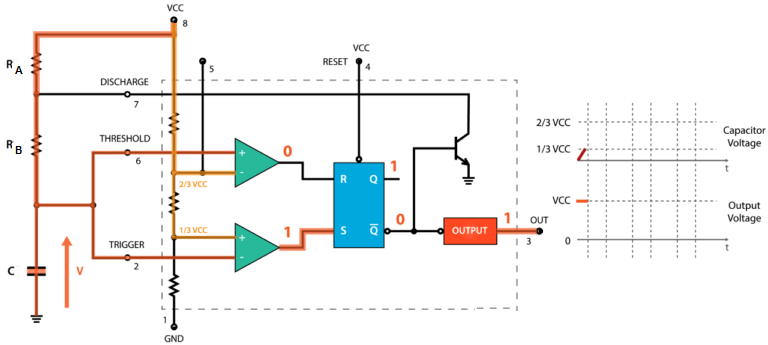

Na fig.7, VC = VPINO6 = VPINO2 , e como inicialmente S = 1 e R = 0, de acordo com a tabela verdade do FF RS temos:

| e Vsaida = VCC. Como o transistor interno esta cortado, o capacitor C começa a se carregar através de RA + RB . |

Quando

VC > VCC/3 ( basta que seja alguns mV maior ) teremos

R = S = 0 o que mantém o estado do FF interno,.isto

é , OUT = 1 = VCC.

Fig.8

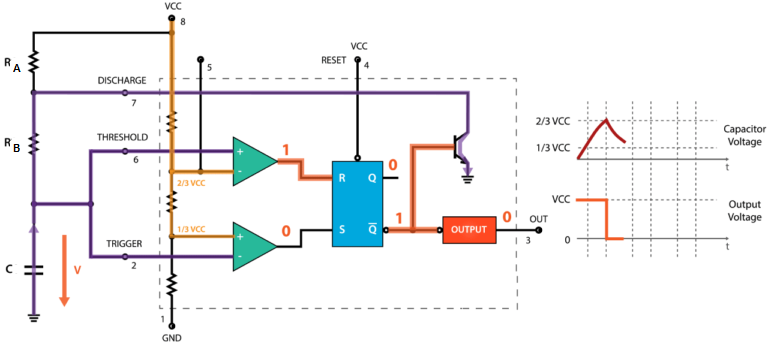

| Quando porém | O Flip Flop resetará, isto é, teremos agora R = 1 e S = 0 |

e nesse instante a saída OUT vai a zero, saturando o transistor interno e fazendo o capacitor C se descarregar através de RB e pelo transistor interno. Veja a fig.9

Fig.9

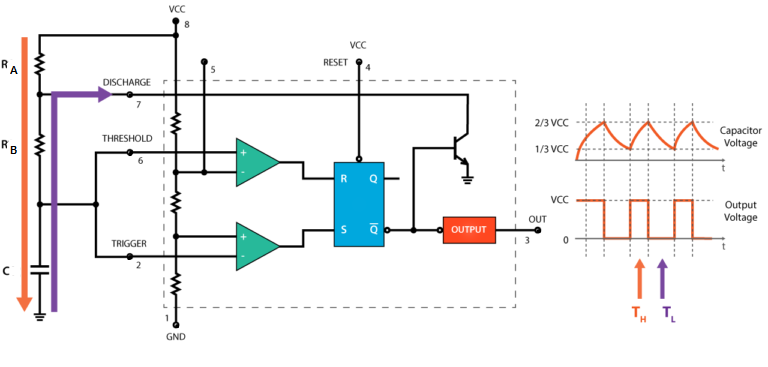

Quando a tensão em C cair abaixo de VCC/3 , novamente teremos S = 1 e R = 0 setando o FF e portanto a saída volta para VCC e o transistor corta fazendo o capacitor se carregar por RA + RB e tudo se repete.Veja a fig.10.

Fig.10

A Fig.11 mostra as formas de onda no capacitor e na saída OUT(pino 3).

|

|

Fig.11- Formas de ondas no capacitor e na saída |

Os tempos alto ( TH )

e baixo ( TL ) são calculados por :

TH

= 0,69.( RA + RB ).C e

TL

= 0,69.RB.C

Observe que o tempo alto é maior que o tempo baixo pois a carga se dá por (RA + RB) e a descarga por RB. Caso se deseje tempos iguais deve-se impor RB muito maior do que RA, sendo que RA deve ter valor de pelo menos 1K para que o transistor interno não sofra danos.

As expressões de TH e TL podem ser generalizadas por :

TH = 0,69.RCarga.C e TL = 0,69.RDescarga.C

Para o circuito da figura 07,calcule TH , TL e o período das oscilações para RA = 5K6 OHM ,RB = 4K7 OHM e C= 100microF