Complementary -

Metal Oxide Semiconductor

Trata-se de uma família que tem seus circuitos construídos por

transistores MOS-FET (Metal Oxide

Semiconductor-Field Effect

Transistor) do tipo canal N e canal

P.

Suas configurações básicas permitem

uma série de vantagens, tais como:

alto Fan-Out, alta margem de imunidade ao

ruído e baixíssimo consumo.

Estrutura

Básica dos MOS-FET Canal N e Canal P

Corrente

de Dreno versus VGS para o MOS-FET Canal N

Corrente

de Dreno versus VGS para o MOS-FET Canal P

Simbologias

Transistores MOS são chaves eletrônicas controladas por

tensão. Os dois tipos básicos são o MOSFET canal N ( NMOS) e o MOSFET canal P ( PMOS ).

A seguir são mostrados os símbolos mais

usados.

Observe que um MOS tem 4 terminais : Gate (G), Dreno(D), Fonte(S) e

Substrato(B).Os símbolos da direita muita vezes são usados para

simplificar a representação do MOS-FET.As

tensões que são usadas para controlar o fluxo de corrente através do dispositivo

são VGS e VDS.

MOS

canal N (simbologias)

NMOS

|

|

MOS

canal P (simbologias) PMOS |

|

|

|

Muitas vezes o eletrodo do substrato é omitido por simplicidade,

e para distinguir entre NMOS e PMOS é usada o círculo no

terminal gate para indicar inversão.

Aplicando uma tensão no terminal gate o

MOS-FET conduz. Um NMOS conduz quando é aplicada uma tensão positiva , enquanto um PMOS conduz

com uma tensão negativa.

|

Transistor MOS-FET como Chave

Um transistor MOS pode ser modelado como sendo

simplesmente uma chave.

O fechamento e a abertura é

controlada pela tensão VGS . Se associarmos o nível lógico "1" a VDD

e o nível lógico "0" a 0V ,quando no NMOS tivermos VGS

= VDD então a chave fecha , no PMOS é o contrário , se VGS

=0V a chave fecha.

Transistor MOS-FET como chave

|

|

| Um

inversor pode ser construído utilizando um NMOS e um PMOS. A saída deve ser alta quando a entrada for baixa e

vice versa.

Como podemos verificar a tensão de entrada ( Ve ) é

aplicada simultaneamente aos dois gates dos

transistores MOS-FET. Para que

a saída seja VDD , o transistor PMOS deve conduzir e

isto é obtido fazendo Ve = 0 V .

Para a saída assumir

0 V,devemos aplicar Ve = Vdd ,desta forma o transistor NMOS deve conduzir enquanto o

PMOS deve estar cortado.

|

|

|

Configuração Inversor C-MOS

|

|

Funcionamento para Ve=0V ( L ) e Ve= Vdd ( H )

|

|

ESTRUTURA FÍSICA - OPERAÇÃO-

A seguir temos um corte de um transistor

MOS-FET canal N :

|

|

O transistor é fabricado em cima de uma base

chamada de substrato ( no caso de MOS canal P essa região é N ).

Duas regiões fortemente dopadas

tipo N são criadas no substrato originando o dreno(D) e a fonte(S de source ).

Uma camada muito fina de cerca de 40nm

de dióxido de silício ( que é isolante ) é criada sobre a região do substrato

entre

dreno e fonte.

No começo, era depositado sobre

esse óxido uma camada de metal ( o M de MOS),

atualmente devido a necessidades

tecnológicas o material é o silício policristalino( polisilicio ) |

A seguir temos o mesmo transistor

MOS-FET em 3D e as duas

principais dimensões do mesmo: Comprimento do canal ( L ) e largura do canal

(W).

|

|

As principais características

elétricas de um transistor MOS são determinadas em função das suas

dimensões (W e L ) e da espessura da camada de óxido em cima do canal.

O comprimento do canal ( L ) é da ordem de 0,18mm,

sendo possível desta forma colocar 5 milhões de transistores num único

chip. A diminuição das dimensões faz aparecer novos desafios , como por exemplo o

desenvolvimento de novos materiais e o uso de outros já conhecidos mas que não

eram usados devidos a algumas dificuldades que agora estão sendo superadas.

Com o avanço nas velocidades de

processamento começaram a aparecer outras alternativas como por exemplo o

transistor SOI ( Silicon On Insulated ), no qual o substrato não é mais um

material semicondutor, desta forma não existem mais junções que

originam capacitâncias parasitas e que limitam a máxima

freqüência de operação. Existem outros semicondutores como o Arseneto de gálio

(AsGa)

que tem características que permite operar em freqüências mais altas

que o Si.

|

|

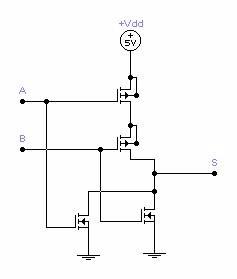

Vamos analisar o funcionamento

dos blocos lógicos principais desta família que são as portas lógicas NOU e NE.

A

figura a seguir, mostra o circuito básico de uma porta NOU CMOS.

Quando ambas as entradas estiverem em 0V (potencial do

terra), os MOS-FET canal P, estarão conduzindo e os Mos-FET canal N, estarão

cortados. Isso fará com que a tensão de saída assuma valor igual a +Vdd (nível

lógico 1). Quando pelo menos uma das entradas estiver em +Vdd (nível lógico 1), teremos

o respectivo MOS-FET canal N conduzindo, fazendo com que na saída tenhamos uma tensão

igual a 0V. Verificando estas situações em uma tabela verdade, concluímos que o

circuito comporta-se como uma porta NOU:

A

|

B

|

|

S

|

0

|

0

|

|

1

|

0

|

1

|

|

0 |

1

|

0

|

|

0 |

1

|

1

|

|

0

|

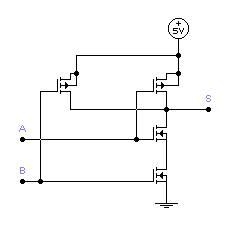

Vamos analisar agora, o

funcionamento da porta NE CMOS.

O circuito básico é visto na figura a seguir:

Quando pelo menos uma das entradas estiver em 0V, o respectivo

MOS-FET canal N, estará cortado e o respectivo MOS-FET canal P, estará conduzido,

logo teremos na saída uma tensão igual a Vdd (nível lógico 1).

Quando ambas as entradas estiverem em +Vdd (nível lógico 1), os

MOS-FET canal N estarão conduzindo, ficando os MOS-FET canal P cortados, logo, teremos na

saída uma tensão igual a 0V. Verificando estas situações em uma tabela verdade

concluímos que o circuito comporta-se como uma porta NE:

A

|

B

|

|

S

|

0

|

0

|

|

1

|

0

|

1

|

|

1

|

1

|

0

|

|

1

|

1

|

1

|

|

0

|

RESUMO das

CARACTERÍSTICAS GERAIS DA FAMÍLIA LÓGICA C-MOS